- 您现在的位置:买卖IC网 > Sheet目录3880 > PIC24F08KL302-I/SO (Microchip Technology)IC MCU 16BIT 8KB FLASH 28-SOIC

CHAPTER 8 8-BIT TIMER/EVENT COUNTERS 2 TO 5

User’s Manual U15905EJ2V1UD

253

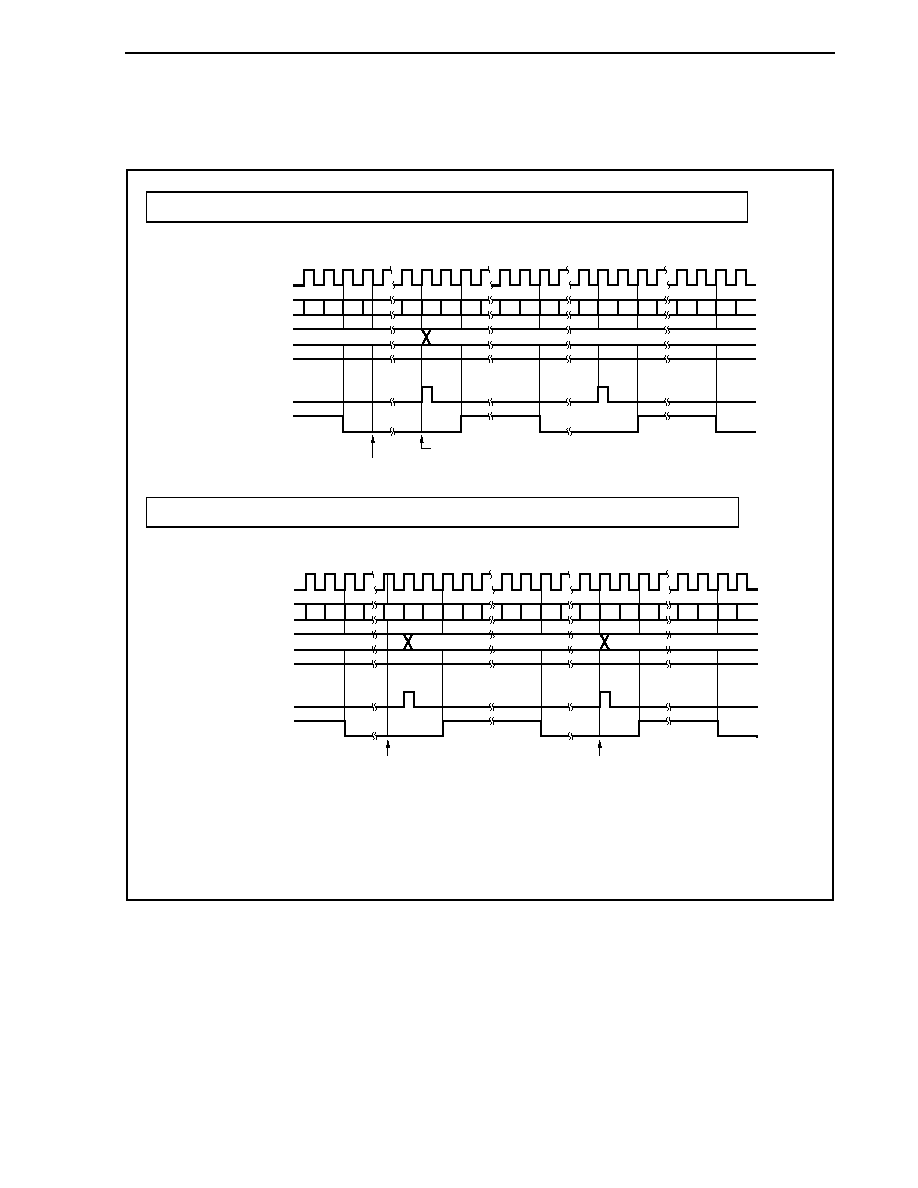

(b) Operation based on CRn register transitions

Figure 8-6. Timing of Operation Based on CRn Register Transitions

When the value of the CRn register changes from N to M before the rising edge of the FFH clock

→ The value of the CRn register is reloaded at the overflow that occurs immediately after.

N N + 1 N + 2

M

N

<1> CRn transition (N

→ M)

M

M + 1 M + 2

M M +1M + 2

FFH

02H

00H 01H

FFH

02H

00H 01H

Count clock

TMn count value

CRn

TMCEn

H

INTTMn

TOn

<2>

When the value of the CRn register changes from N to M after the rising edge of the FFH clock

→ The value of the CRn register is reloaded at the second overflow.

N N + 1 N + 2

N

NN

<1> CRn transition (N

→ M)

M

N + 1 N + 2

M M + 1 M + 2

FFH

03H

02H

00H 01H

FFH

02H

00H 01H

Count clock

TMn count value

CRn

TMCEn

H

INTTMn

TOn

<2>

Caution

In the case of reload from the CRn register between <1> and <2>, the value that is actually

used differs (Read value: M; Actual value of CRn register: N).

Remark

n = 2 to 5

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2L-0535-1

CONN FPC 5POS 0.5MM SMT

PIC18LF23K22-I/SS

IC PIC MCU 8KB FLASH 28SSOP

PIC16LF1933-I/ML

IC PIC MCU FLASH 4K 28-QFN

PIC16F1933-I/ML

IC MCU 8BIT FLASH 28-QFN

PIC16F785-I/ML

IC PIC MCU FLASH 2KX14 20QFN

XF2L-0425-1

CONN FPC 4POS 0.5MM SMT

PIC16F1933-I/MV

IC MCU 8BIT FLASH 28-UQFN

PIC16F785-I/SO

IC PIC MCU FLASH 2KX14 20SOIC

相关代理商/技术参数

PIC24F08KL302-I/SP

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/ML

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/MQ

功能描述:16位微控制器 - MCU 8KB FL 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL401

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low-Power, Low-Cost, General Purpose 16-Bit Flash Microcontrollers with nanoWatt XLP Technology

PIC24F08KL401-I/MQ

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT